1.11 Microprocessor- Multicore and Multithreading

- ⭐️ concept of multicore, multi thread

- ⭐️ FSB, BSB

- ⭐️ memory controller

- ⭐️ transport bus

- ⭐️ GPU

✅ Multicore

- CPU is multicore if the

neumann machineis replicated several times - However, even if replicated, not all blocks are replicated

✔️ In CU

clock, sequencer is NOT replicated

clock: NOT replicated❌ we need only one bosssequencer: NOT replicated❌ only one clock, only one sequencer to set only one rythmProgram counter: Replicated⭕️ each core has onePC, every core can run own instuctions, everyPCpointing to their own address and has each has own instructions, this is multi-taskingInstruction Register: Replicated⭕️ as each core has eachPCDecoder: Replicated⭕️ to helpIR

✔️ In ALU

ALL replicated

InRAandInRA: Replicated⭕️Operational Circuit: Replicated⭕️ACCUM: Replicated⭕️State Register: Replicated⭕️- 👉🏻 Thus, all

ALU blocksare replicated - bc all the instructions use different numbers

- 👉🏻 Thus, all

✔️ In MU

RAM is unique

Memory Controller

- The

RAMis unique, outside the micro-processor - thus the

RAMis NOT replicated❌ - However, as 4 instructions are running at the same time,

MAR,MDRandMSwill be more stressed! - 4 instructions will come at the same time

- 😫 So

RAMis unique, but the internal blocks(MAR,MDR,MS) will be more stressed - 💊 Memory Controller: So we have a super block

- So instead of having

MAR,MDR,MS, we haveONE BIG BLOCKfor controlling everything - This huge block works simillar to replicating the

RAM blocks(MAR,MDR,MS), and reduces the stree of theRAM - sometimes, next to the

Memory Controller, there is aSystem Agent block - System Agent block: to help coordinate several

RAMs When you have several

RAMs, theSystem Agent blockhelps coordinating thedivided RAM- In the picture, there are

4 cores, so there are4 neumann machines - So if we have

4 cores, we will have- one clock, one sequencer

- 4

PCs,IRsandDecoder, all blocks ofALU blocks

- if we have

4 coreswe can run 4 instructions at the same time simultaneously - And we have one RAM, but we have

Memory Controller

✔️ In Peripherals

Transport Bus

- 😫 In multicore, the peripherals are also collapsed, very stressed running several instructions at the same time

- 💊 Transport Bus(also called Input/Output memory controller (I/O))

- used for controlling the peripherals at a very high speed

- ⭐️ In the exam, this block will be called

Transport Bus⭕️, and NOTInput/Output memory controller❌

☑️ Graphics Processing Card

- If we are multicore, there can be a portion named

GPU - however, not mandatory

- helps the other standard graphics card with the graphics(images, videos)

- 🛠️ For games, music, movies

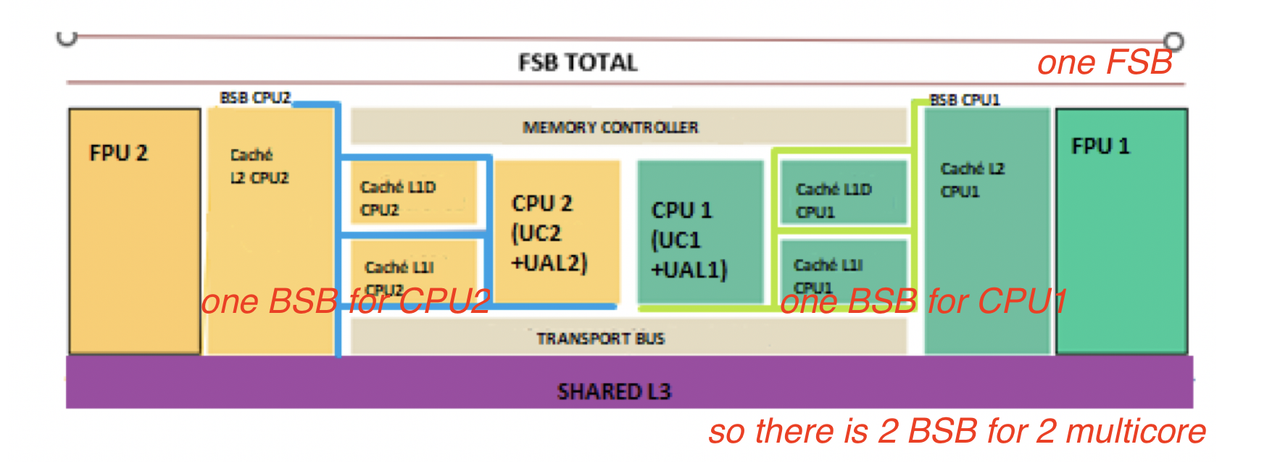

✅ Back Side Bus BSB

road inside core

- Each core inside has an internal sturcture for communication

- like internal streets/roads

- ⭐️ one

BSBper core - one core will have their own

BSB - 🐢

BSBis relatively slower toFSB

1

2

3

4

5

❓ If in core 3, the data from InRA is 3,

but cannot reach the OC,

what is the problem?

A: The BSB in core 3 is broken, having problems.

✅ Front Side Bus FSB

road to communicate among cores

- Apart from

BSB, there is a circular highway to communicate AMONG cores - circular road to connect all the cores

- ⭐️ there is only ONE

FSBin one computer

1

2

3

❓ In 4 core computer, how many BSB and FSB?

A: There will be 4 BSBs and 1 FSB

- Sometimes, we have to send information from one core to another

- 🛠️ Then we need to use

FSB

1

2

3

❓ If the result of operation 1 in core 1 cannot reach InRB of core 4, what is the problem?

A: The FSB is not working properly.

✔️ Speed of FSB

- 🐇

FSBis the fast speed bus - If my clock has 2GHz, my

FSBtends to be2GHztoo so the

FSBhas more or less same speed as the clock- If the clock is much faster than the

FSB, it means there is a bottleneck in theFSB - example: If my

clock is 2.5GB, and myFSB is 1GHz

✅ How many cores?

- In computing, every number should be a

power of 2 1 core: mono-core- However, sometimes core is not a

power of 2, for example:6 core computer - then, it means

4 coreand2 coresare for mirroring - 🛠️ for protection, backups

1

2

3

4

❓ In a 8 core computer, what is the result of this?

FSB + BSB + MC + TB

= 1 + 8 + 1 + 1

= 11

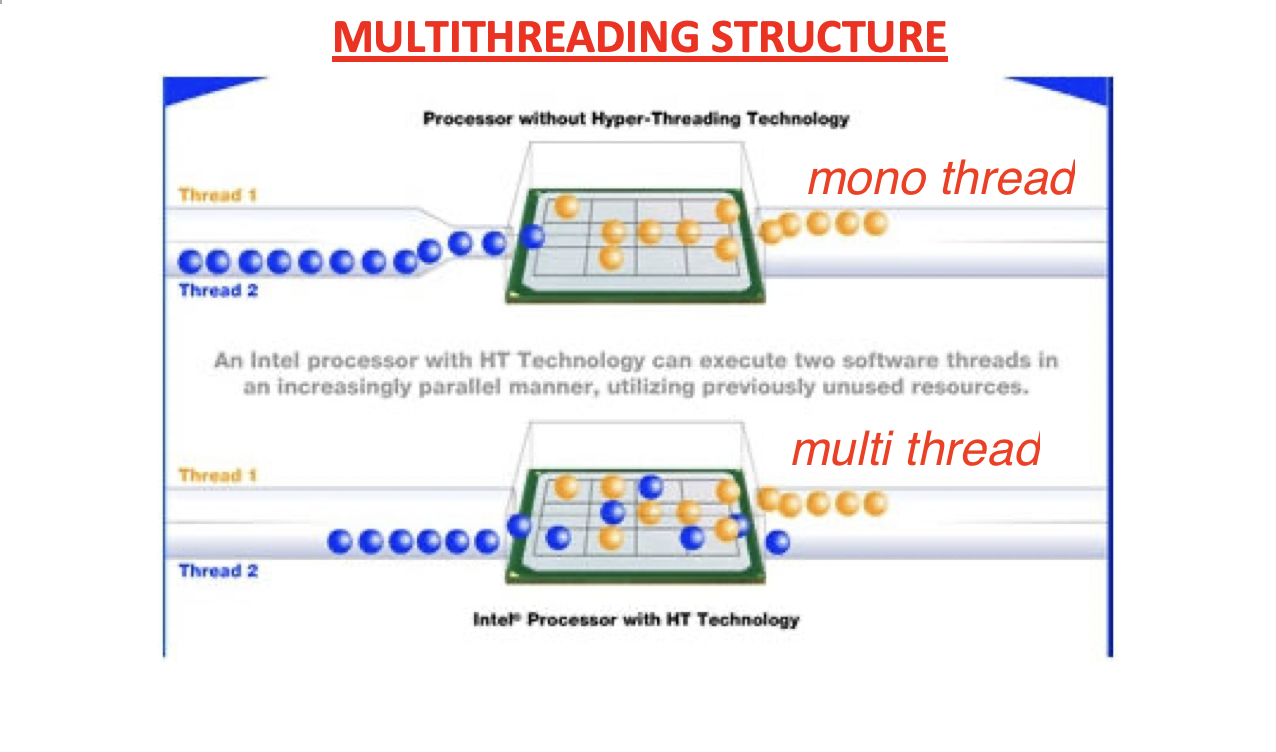

✅ Multi-thread

Dividing one process into several execution threads

- each of the threads(parts of process) will be processed by different blocks

- If you want your job to be done without interruption/disconnection

- use an independent execution thread

✔️ Resource sharing in multi-thread

- being multi-threading means more or less multi-tasking

you can only do multi-threading if you have a resource sharing technique

Mono thread: takes the whole micro processor to itself- yellow runs, then blue

Multi thread: the threads have to share the micro processorThe microprocessor would do blue and yellow at the same time

- If I am multi-core, it is easy to be multi-thread

- If you have many cores, it does NOT necessarily mean your computer is faster ❌

- It means your computer can run more things at the same time

- It means your computer micro processor is more stressed, more hotter, need to ventilate more, need to refresh your computer more

✔️ Optimization

- If you are mono-core you can be multi-thread ⭕️

- But you have to share your resources very well

- 💊 Optimization tools: help share resources among threads in mono-core

✅ Logic Core

Physical core: number of cores we have,8 core = 8 physical coreThreads per core: how many thread in a coreLogic cores: how many threads I have in total

1

2

3

4

5

6

7

8

9

10

❓ If we have 4 cores, and each core executes 2 threads, how many threads in total can we execute?

A: 8 threads in total

Physical core: 4

Threads per core: 2

Logic cores: 8

I have a computer of physical core of 4, thread per core is 2

then I have 8 logic cores

⚠️ I have 4 physical cores, but have 8 logic cores, bc I feel like I have 8 workers!

✅

✅

This post is licensed under CC BY 4.0 by the author.